## **RTDS Simulator**

## MMC (Multi-Module Converters) Modeling

MMC (Multi-Module Converters) offer many advantages compared to conventional thyristor based schemes and are becoming widely in HVDC FACTS and used They also present applications. significant challenges for modeling Electro-Magnetic Transient with techniques. (EMT) simulation However RTDS Technologies has developed a number of models during the past several years to overcome these challenges. Three

models are presented below. All three models are small timestep sub-network components which allows great flexibility of configuration as well as very low loop delay between the real time simulation and external controls.

**FPGA-Based MMC:** The latest MMC development from RTDS Technologies is an FPGA based component that is fully integrated into the small timestep sub-network providing valuable modeling flexibility with detailed representation of up to 512 submodules per valve or more than 3000 submodules per HVDC station! The model is used for detailed control development and detailed factory acceptance testing where a physical connection to external firing pulse controls is required. The FPGA-based model supports various internal faults for in-depth control testing.

**CHAINV5:** The CHAINV5 model uses the same algorithm as the FPGA-based model described above, but it is a processor based model (i.e. it is simulated using a PB5 or GPC processor). CHAINV5 can support 40 / 50 levels in the full / half bridge configuration and it is designed to test the actual firing pulse controls.

**MMC5:** The MMC5 model is designed to study and test high level control and uses a simplified control interface (i.e. it does not take in firing pulses as input). The input to the model is number of deblocked submodules and the number of positively or negatively inserted submodules. MMC5 can represent more than 600 levels per valve (1200 per phase - 3600 per HVDC station).

## MMC Modeling

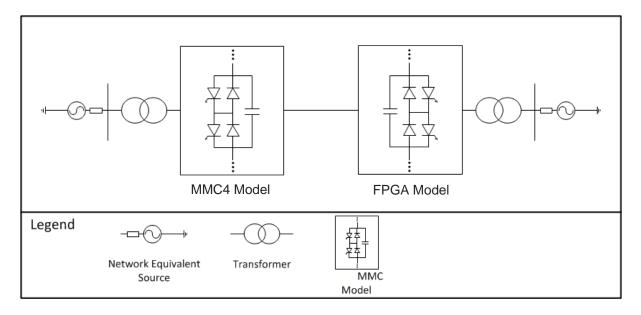

## Demonstration Case MMC-Based HVDC Using MMC5 and FPGA-Based Model

The MMC-based demonstration includes a 2-terminal HVDC scheme. The MMC valves each contain 512 submodules. The valves at one end of the scheme are modeled using the MMC5 component while the valves at the other end are modeled in full detail using the FPGA-based component. Two MMC Support Units represent the FPGA-based valve models while three other MMC Support Units provide the capacitor voltage balancing and firing pulse control for the terminal. The high level control for the HVDC scheme is represented using PB5 processors.

As mentioned above, not only are six MMC valves represented using FPGA's, but also their respective capacitor balancing and firing pulse controls. The MMC Support Units representing the valves are connected to the MMC Support Units containing the firing pulse controls via optical fibre. The valve models calculate the valve current and the capacitor voltage for each level and send it to the controller. The control in turn provides the firing pulses for each level. The signal exchange uses a standard serial protocol known as Aurora which can be adopted and used for the connection of any external controller.